# Connect the World by lighting the way — the essential link in next-generation optical connectivity

3D Lithography is lighting the path toward scalable and reliable processes for integrating active components into PICs

# **Vanguard Automation** on a Page

Unique IP and Fully Automated Tool Chain for Photonic Interconnects

#### 2018

Joint Venture between KIT Spin-Off and ELAS Technologies GmbH – headquartered in Karlsruhe, Germany

#### 2024

Joined Mycronic AB (publ) Swedish high-tech group

MYCRONIC

# **Unique IP**

Growing patent families in the field of 3D lithography and photonic packaging

#### **Products**

Process technology incl.

Systems, Software,

Consumables, related

Support and Services

#### 50+

Employees (17 nationalities)

vanguard

AUTOMATION

MYCRONIC

# **Photonic Integrated Circuits are Growing Rapidly**

Telecom/ Datacom

AI/Optical Computing

Sensing

Quantum Technologies

Space & Defense

#### **Mission**

"Building upon unique IP and expertise in photonics packaging, we empower research and industry to design and manufacture next-generation optical devices through automated solutions that overcome design, performance and scalability challenges."

# **Today's Packaging and Assembly Challenges**

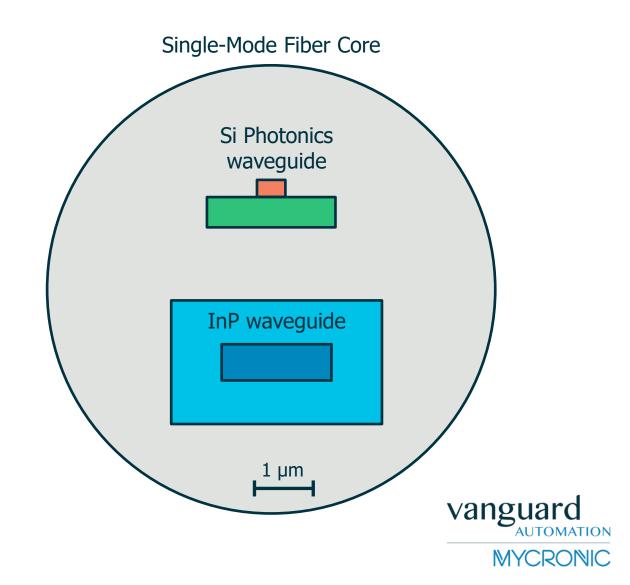

Different Mode Field Sizes and Heterogenous Material Platforms

Mode field matching

High-precision assembly alignment

Fast and reproducible packaging

Reliable under various conditions

About 80% of the cost of photonic integrated systems are generated by the packaging process

# Enabling Next Generation Photonic Integration and Packaging Solutions with 3D Laser Lithography Solutions

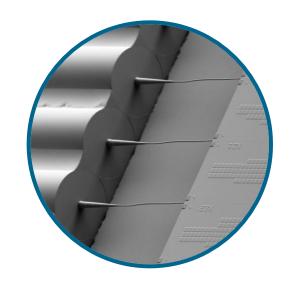

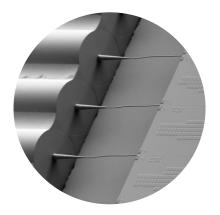

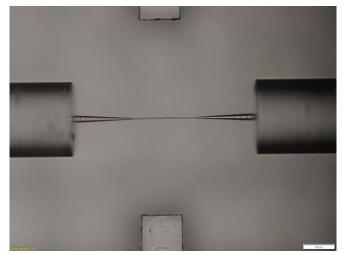

#### **Photonic Wire Bonding (PWB)**

**Low loss** connections to arbitrary mode fields

Automated, reproducible and fast

**Reliable** connections under various conditions

**High interconnect density** (compact modules)

High degree of **design flexibility** for hybrid multi-chip integration

# Unique Solution to Photonic Packaging and Integration

### Industry-Grade 3D Nano-Printed Photonic Interconnects

#### **Limited Scalability**

#### Performance, Scale, Design Flexibility

#### Complexity

Lens Active Alignment

Current devices are built with

active alignment. Limits

miniaturization and increases

overall package size.

3D in-situ nano-printed lenses allow parallel optical connections in a much smaller form factor. Improves coupling efficiency and increases Yield

GT-PI

**Micro-Optical Lenses**

Fast, low loss connections between known-good components. No alignment, no lenses, smaller packages, enabling new designs.

GT-PT

**Photonic Wire Bonds**

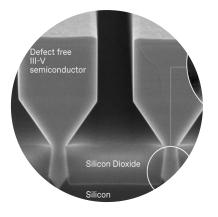

Heterogenous Integration

Direct laser integration on silicon

SOI wafer. Locked into specific

components, long

development times, lower

yields.

# PPA Metrics: Techniques for **Integrating a Laser into a Silicon PIC**

S. Sekhar, W. Bogaerts, L. Chrostowski, et al., Roadmapping the next generation of silicon photonics, 2024

|                      |                                | <b>←</b> →                             | <b>— —</b>                | <u></u>                          | <del></del>                         | <b>←</b> →                         |

|----------------------|--------------------------------|----------------------------------------|---------------------------|----------------------------------|-------------------------------------|------------------------------------|

| Integration          | Conventional<br>LD-ISO-FAU-PIC | <b>Hybrid 2.5D</b><br>FSO <b>→FaML</b> | <b>Hybrid 2.5D</b><br>PWB | <b>Hybrid 3D</b><br>Flip Chip/TP | <b>Heterogenous</b> Dir. Bonding/TP | <b>Monolithic</b><br>Heteroepitaxy |

| <b>Coupling loss</b> | > 2 dB                         | 0.3 dB                                 | 0.5 dB                    | 1 dB                             | 1 dB                                | Few dBs                            |

| <b>Output power</b>  | High                           | High, <b>1 W</b>                       | High, <b>500 mW</b>       | Medium                           | Medium                              | Low                                |

| Pol. ctrl.           | Needed                         | Needed                                 | No need                   | No Need                          | No Need                             | No Neeed                           |

| Therm. mngt.         | Easy                           | Easy                                   | Easy                      | Medium-Difficult                 | Difficult                           | Medium                             |

| Linewidth red.       | N/A                            | Good- <b>Best</b>                      | Good- <b>Best</b>         | Good                             | Best                                | Good                               |

| Assembly size        | Large                          | Medium- <b>Small</b>                   | Medium-Small              | Small                            | Smallest                            | Smallest                           |

| On-chip              | No                             | No- <b>Yes</b>                         | No- <b>Yes</b>            | Yes                              | Yes                                 | Yes                                |

| Pckg. style          | KGD                            | KGD                                    | KGD                       | KGD                              | All or nothing                      | All or nothing                     |

| Test                 | Die                            | Die-Wafer                              | Die-Wafer                 | Die-Wafer                        | Wafer                               | Wafer                              |

**PWBs and FaMLs**

## Towards Standardized Process, Application, and Manufacturing Design Kits

**Initial Insertion Losses** ∼ **1.5** dB

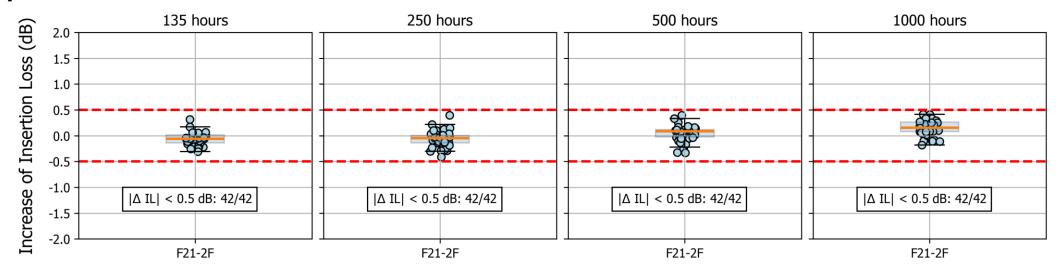

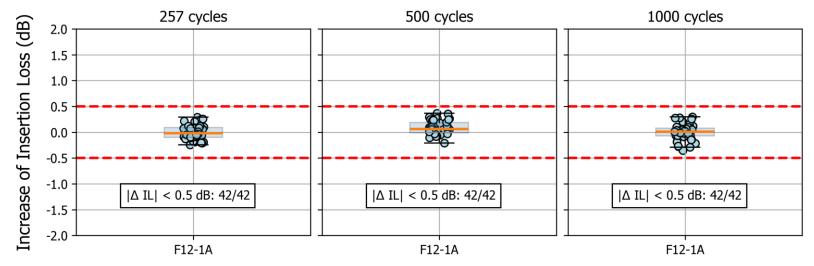

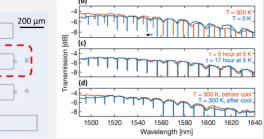

# Reproducibility & Reliability: Photonic Wire Bonding

#### Damp Heat 85°C and 85% RH

#### **Temperature Cycle -40°C to +85°C**

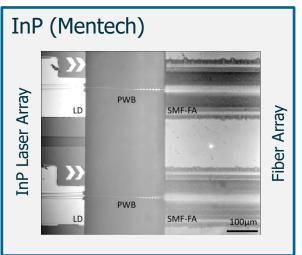

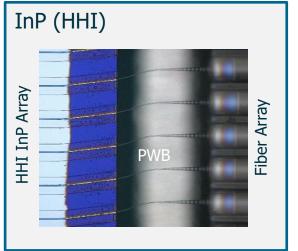

# Industry Proven Photonic Integration and Packaging

Fully Automated Solutions with 3D Laser Lithography

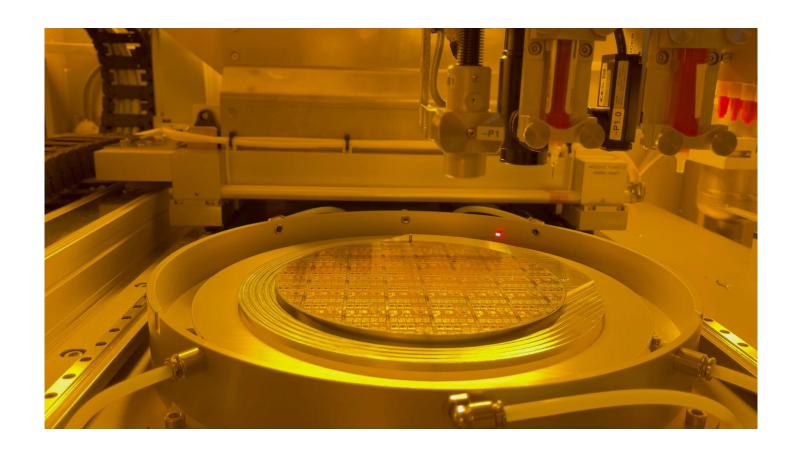

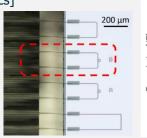

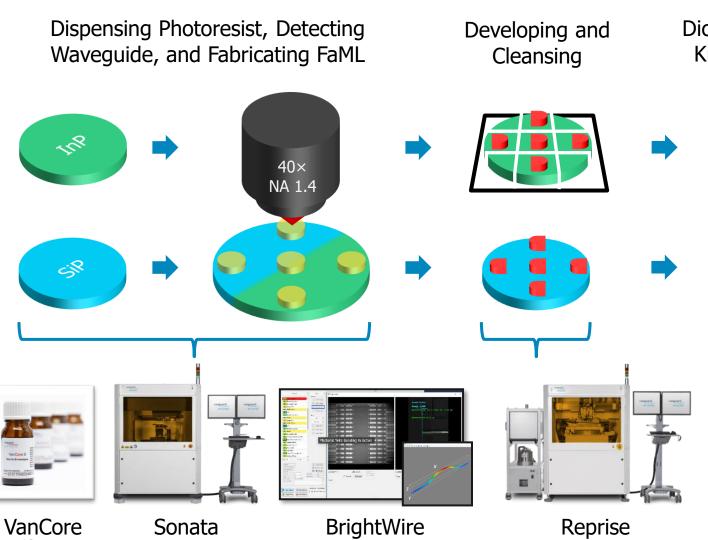

# Wafer Level & Batch Processing for Photonic Integration

Active Device Integration

High Reliability & Yield

Mode-field-matching

Relaxed Pick & Place

Tolerances

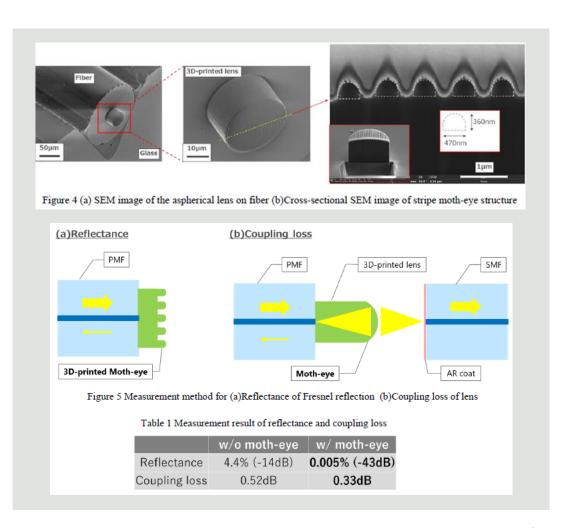

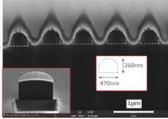

# **3D-printed** aspherical lens with moth-eye anti-reflection structure

"3D-printed aspherical lens with moth-eye anti-reflection structure",(2024)

Y. Mizuno et al., Proc. SPIE 12898, Advanced Fabrication Technologies for Micro/Nano Optics and Photonics XVII, 128980R

**Reflectance on the lens surface was reduced** from 4.4% to 0.005% at 1550 nm wavelength

**Coupling efficiency** to fiber is **improved** from -0.52 dB to -0.33 dB

Structure size 360 x 470 nm

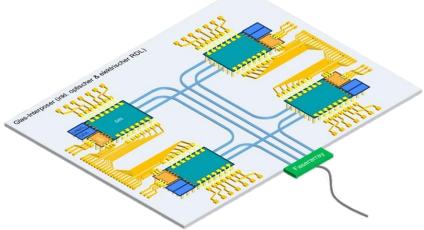

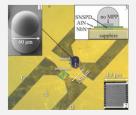

# Recent Quantum Applications from Ecosystem Partners & Users

## SPOC - Scalable Packaging for All-Optical CV Quantum Computing

https://www.izm.fraunhofer.de/en/news\_events/tech\_news/spoc.html

**Glass-based** fully optical **quantum processor**.

Photonic integration of optical chips and fibers by **photonic wire bonding**.

Increased coupling efficiency by **50%**.

### Use Cases – 3D-Printed Lenses

#### **Relaxed Alignment Tolerances**

#### **Maximize Coupling Efficiency**

#### **Low Back Reflectance**

"3D-printed Beam Expanding Lens for Chip to Fiber Vertical Coupling",(2024) Y. Mizuno et al., 2024 IEEE 74th (ECTC), Denver, Colorado, USA)

**Vertical coupling**

Wide bandwidth (1260 to 1575 nm)

**Relaxed alignment** tolerance  $\pm 10 \mu m$

**SUMITOMO**

**1.2dB** coupling efficiency

**Connect with Innovation**

**Collaboration** to incorporate 3D-lithography technology into POET's Optical Interposer $^{\text{TM}}$  platform.

"3D-printed aspherical lens with moth-eye anti-reflection structure",(2024) Y. Mizuno et al., Proc. SPIE 12898, Advanced Fabrication Technologies for Micro/Nano Optics and Photonics XVII, 128980R

**Reflectance** on the lens surface was reduced to **0.005%**

Coupling efficiency to fiber is improved to -0.33 dB

Structure size 360 x 470 nm

#### **Quantum Applications**

Cryogenic temperatures | No degradation | Broadband working range 530 – 2000 nm

"Superconducting nanowire single-photon detector with 3D-printed free-form microlenses", Opt. Express 29, 27708-27731 (2021)

The paper demonstrates FaMLs operating at cryogenic temperatures down to 4.6K

Assemblies undergo 10 cool down cycles

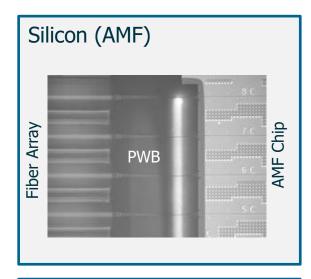

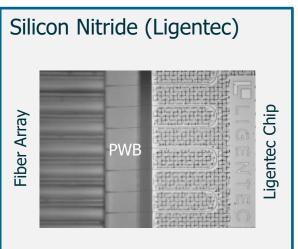

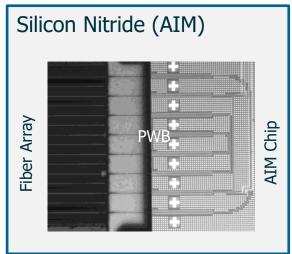

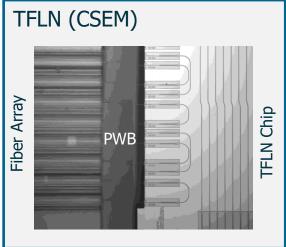

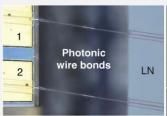

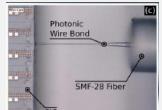

# Use Cases – Photonic Wire Bonding

#### **Active Device Integration**

Multi-Chip Hybrid Integration | Passive alignment process | Mode-field-matching | Relaxed pick and place tolerances of  $\pm$  30  $\mu$ m

"High-power and narrow-linewidth laser on thin-film lithium niobate enabled by photonic wire bonding", Franken et. al. APL Photonics 1 February 2025; 10 (2): 026107

"Packaged Tunable Single-Mode III-V Laser Integrated on a Silicon Photonic Integrated Chip Using Photonic Wire Bonding",(2024) Deenadayalan et al., IEEE 74th (ECTC), Denver, Colorado, USA)

"SiEPICfab: the Canadian silicon photonics rapid-prototyping foundry for integrated optics and quantum computing",(2021) Darcie et al., Proc. SPIE 11691, Silicon Photonics XVI

#### **Quantum Applications**

Cryogenic temperatures | (IL) < 2dB | No degradation

"Cryogenic Optical Packaging Using Photonic Wire Bonds", (2023)

arXiv:2307.07496v1 [physics.optics]

"Plug-and-Play Fiber-Coupled Quantum Dot Single-Photon Source via Photonic Wire Bonding", Adv Quantum Technol. 2023, 2300227

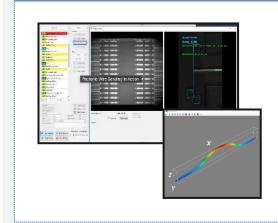

# Vanguard **SYMPHONY 1000**

Unique IP and Fully Automated Tool Chain for Photonic Interconnects

#### **Machines**

# SONATA 1000

Automated 3D Lithography-based Nano Printing

#### REPRISE 1000

Automated Pre- and Post-Processing: Development and Encapsulation

#### **Software**

#### Composer and BrightWire3D

Software for Machine Control, Process Development and Management

#### **Materials and Services**

#### **VanCore Resist Series**

Materials for the production of PWBs and Micro Optical Lenses

#### **Professional Services**

- Training

- Process Development

- Feasibility Studies

- Development Support

- Maintenance Services

#### **COMPLETE INDUSTRY READY SOLUTION**

# Collaborative Ecosystem: Partners and Users

ficontec

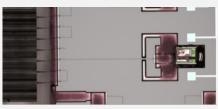

# **3D Lithography** for Photonic Packaging

Strategy 1: PWB for Die-Level Hybrid Integration

- Passive alignment

- Up to  $\pm$  30 µm component placement offset (all axes)

- Mode field adaptation and low insertion loss

- High interconnect density

100 µm

VanDam & VanClad

Reprise

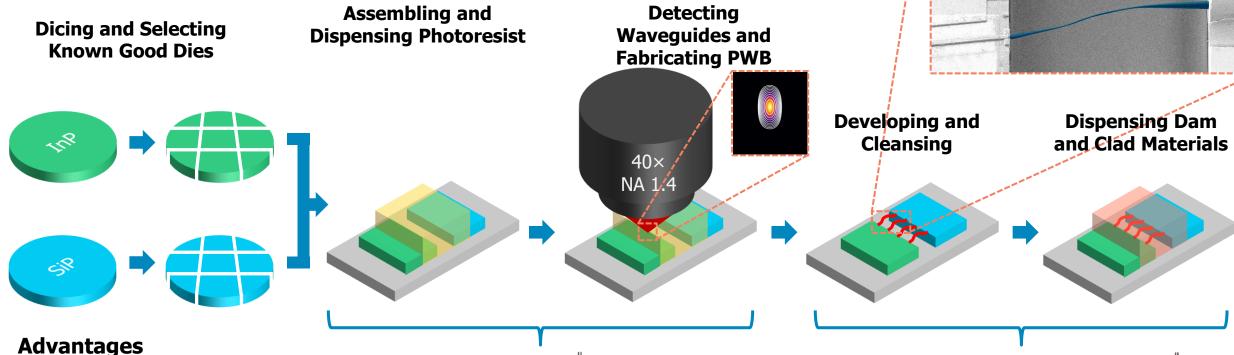

# **3D Lithography** for Photonic Packaging

Strategy 2: FaML for Wafer-Level Hybrid Integration

Dicing and Selecting Known Good Dies

- Accommodates flip-chip approach

- Placement tolerance up to ±15 µm, enabling passive alignment

- Wider distance between components to facilitate bulk optics (e.g., isolator)

25 µm