# Co-Packaged Optics: Technical Barriers and the Road to Mass Production

Swissphotonics Lunch Chat October 14th, 2025

Emma Xu

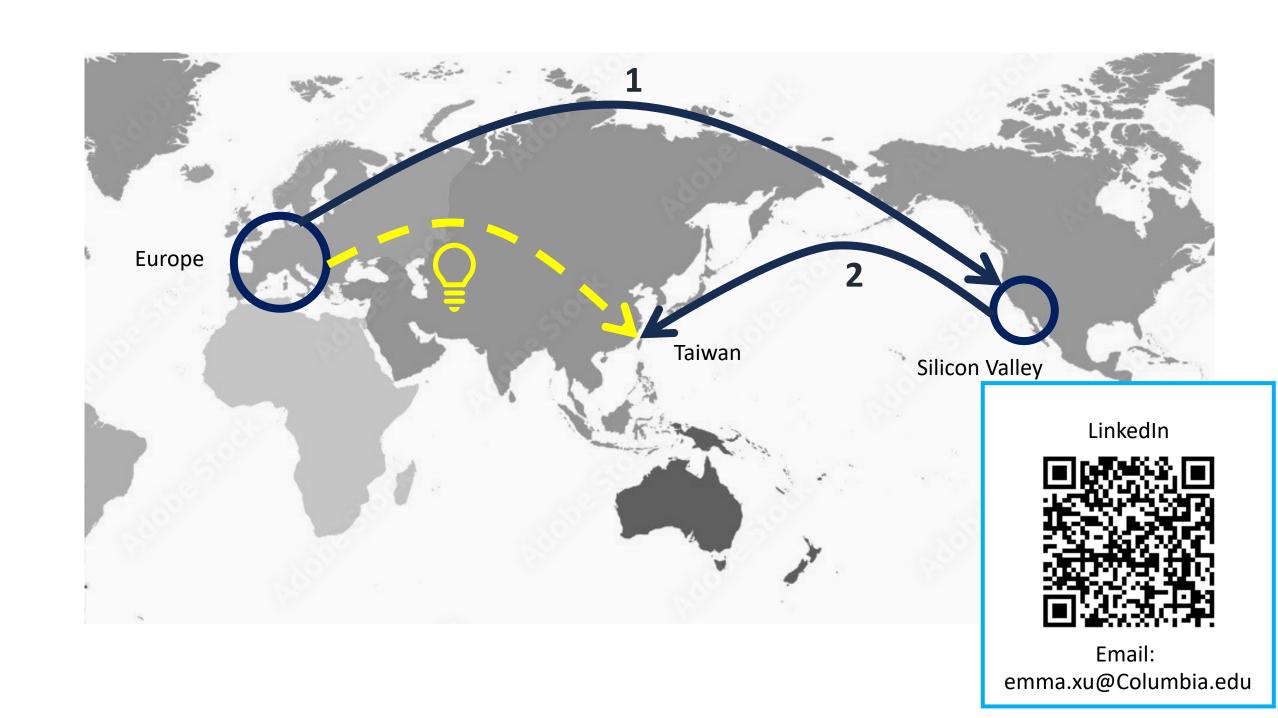

#### About me

- PhD from Columbia University, research topic: photon upconversion & photon avalanching

- 2 Nature publications, 5 patents pending. Former founder; Forbes 30 under 30

- Worked in the US & Germany (semiconductor & photonics industries)

\_\_\_\_\_

Collaborator in Taiwan: Vincent Ho, 30+ years in the semiconductor industry

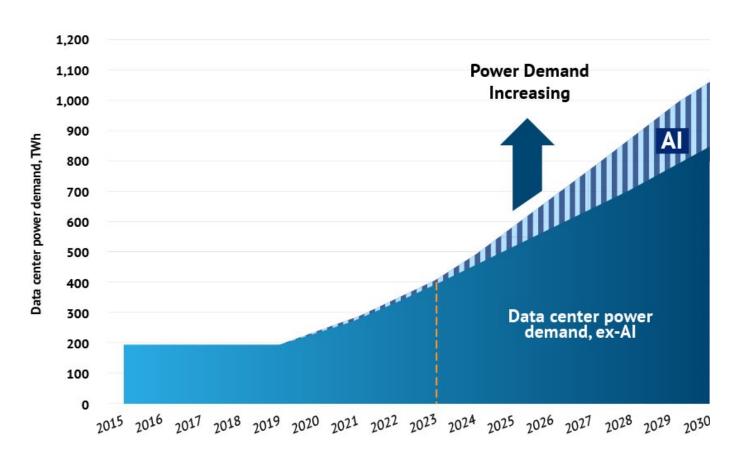

## Motivation: Data centers demand high power

- Current state-of-the-art: data transmitted via copper (electricity)

- With Silicon Photonics:

- higher data throughput

- Lower power consumption

- Mitigate latency

Source: Masanet et al. (2020), Cisco, IEA, Goldman Sachs Global Investment Research

# Co-Packaged Optics (CPO)

**Top View Package Engine Data Speed Side View Pluggable Transceiver Optics QSFP (Quad Small** Pluggable Module **QSFP** ASIC Form-factor Pluggable) **Electrical Path** System Board 100/400/800G Higher bandwidth / Lower power **On-Board Optics** ----OE (Optical Engine) Adapter BGA/LGA OE 800G/1.6T System Board --co-Packaging Optics Advanced 3.2/6.4/12.8T **Packages** System Board Optical I/O Advanced 6.4/12.8T & beyond **Packages** System Board

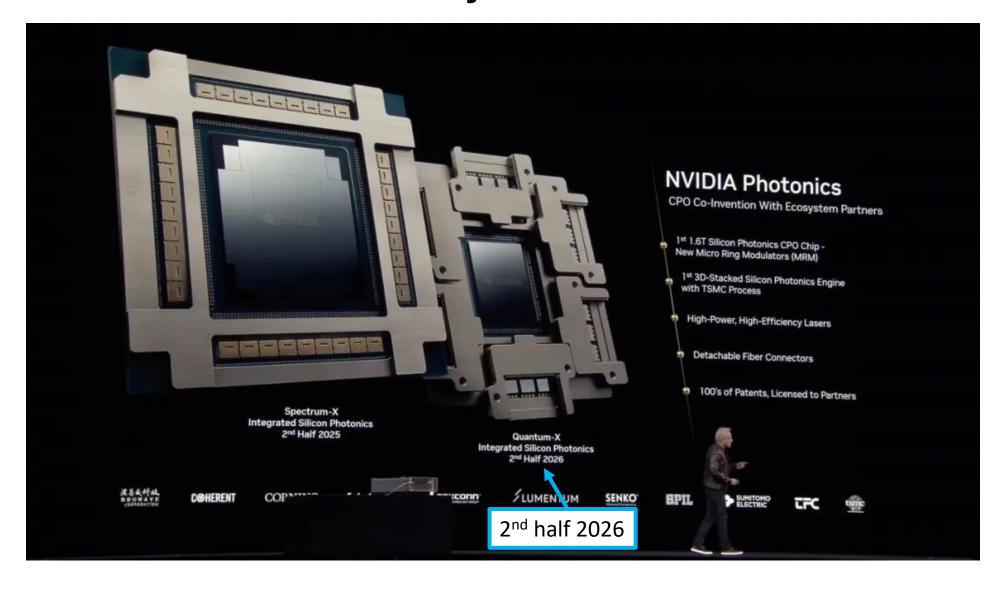

# Nvidia GTC2025 Keynote

## Nvidia CPO-Based Switch

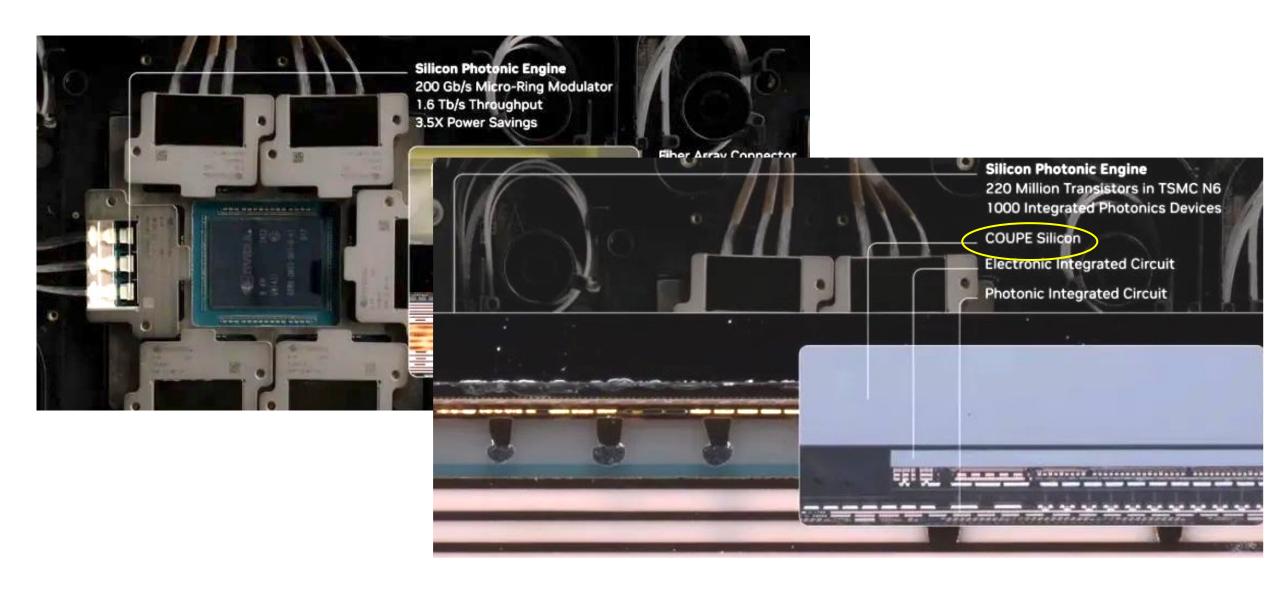

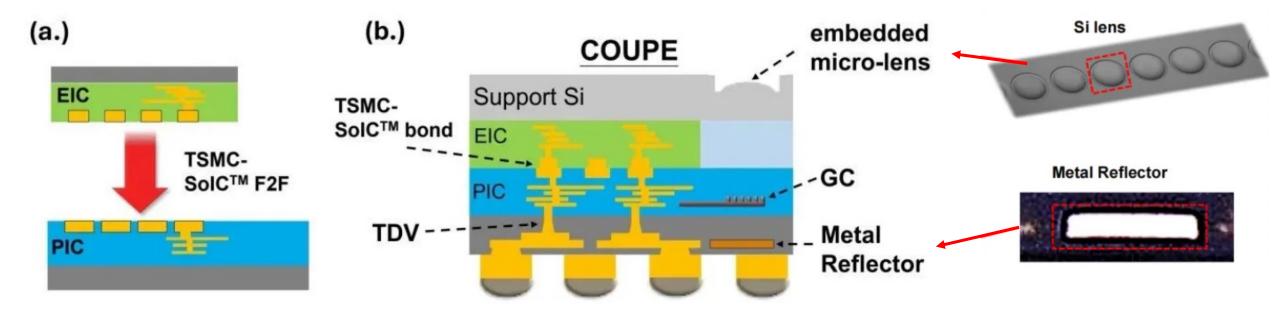

#### TSMC COUPE

(COUPE: compact universal photonic engine)

- TSMC-SoIC face-to-face (F2F) technology for EIC and PIC bonding.

- critical components of COUPE are the TSMC-SolC'" bond, TDV, embedded micro-lens, and metal reflector

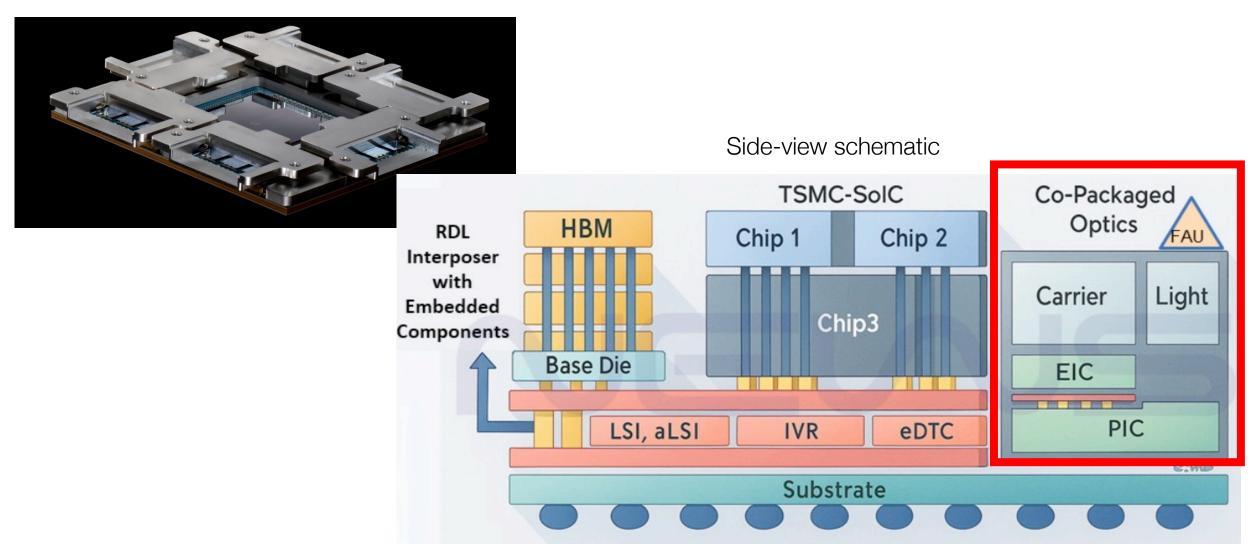

## COUPE + COWOS (COWOS: chip on wafer on substrate)

## COUPE Specs

- High-Performance Silicon Photonics Platform

- 12-inch 65nm silicon photonics platform

- 10um alignment tolerance, 0.3dB loss vertical coupling

- 76GHz micro-ring modulator

- 4.5nA dark current 110GHz GePD

- 1.5nm center resonance wavelength drift (wafer-level control)

- Optoelectronic Integrated Chiplet & CPO

- <1dB/m single-mode SiN waveguide transmission loss</li>

- 0.1dB broadband edge coupler

- 2D fiber array with micro-lenses

- 97% precision in optical beam deflectors

- Parallel Digital Optical Computing Chips

- 4-layer SiN platform

- 512x512 optical computing array, 35dB insertion loss

- 8-bit accuracy computing

- 0.08 pJ/MAC energy efficiency

#### Concerns:

- 1.Cost

- 2.Risk

- 3.Sole supplier

#### Taiwan semiconductor market

- 2024 Taiwan's semiconductor output value = 165 \$Bn, equivalent to 25% of the global value

- 2025 Taiwan's output is projected to 191 \$Bn, 28.1% of global share

| Taiwan IC Industry market share (unit: \$Bn) |       |       |       |       |       |

|----------------------------------------------|-------|-------|-------|-------|-------|

|                                              | 2021  | 2022  | 2023  | 2024  | 2025  |

| Global                                       | 556   | 604   | 526.9 | 655   | 701   |

| Taiwan                                       | 127.1 | 150   | 135.2 | 165.6 | 197   |

| share                                        | 22.9% | 24.8% | 25.7% | 25.3% | 28.1% |

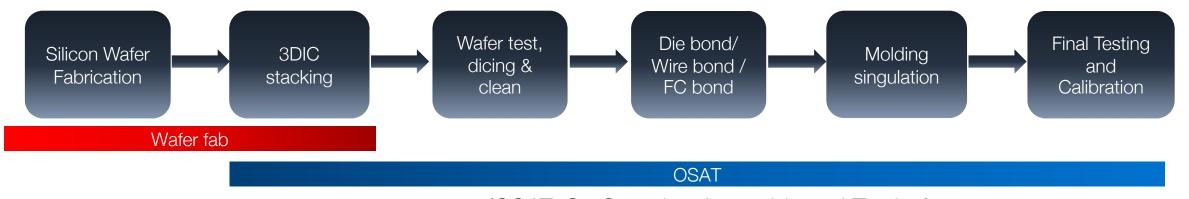

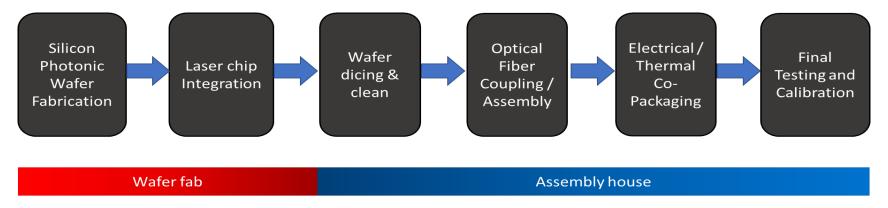

#### Semiconductor Process

(OSAT: OutSourcing Assembly and Testing)

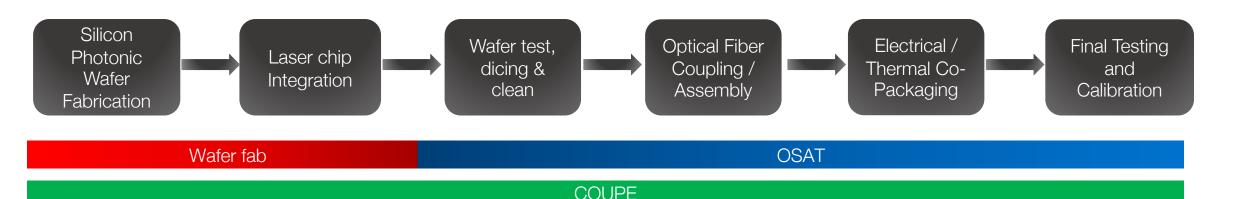

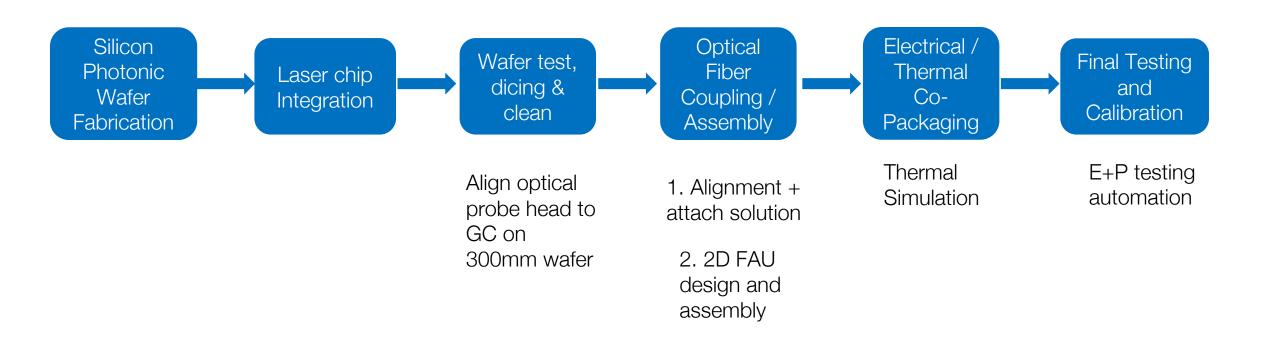

#### Process from SiPh to CPO

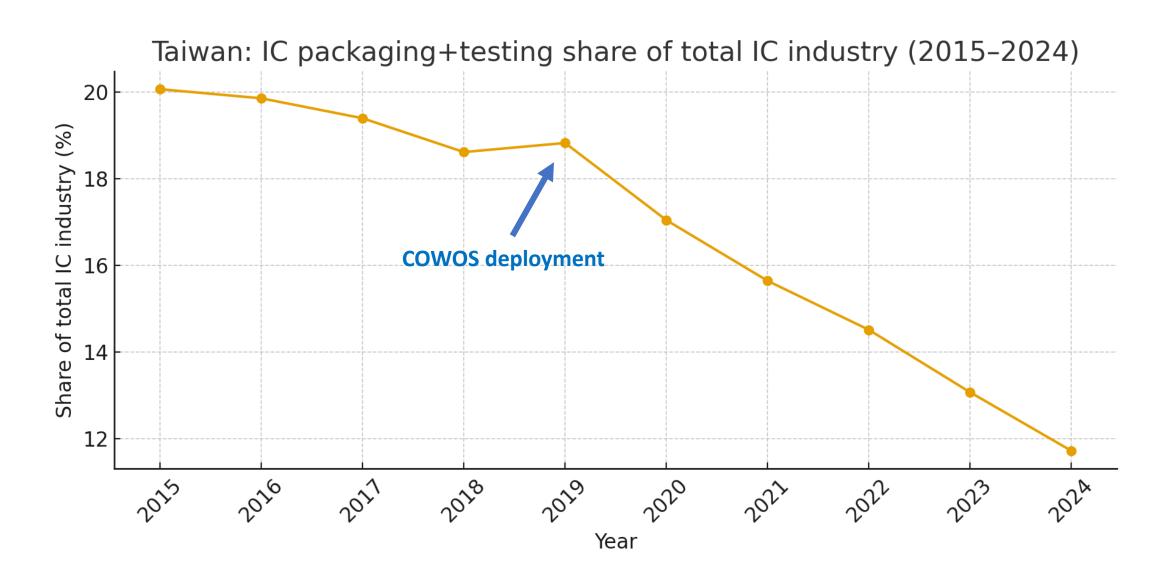

## Taiwan OSAT market share trend

# A packaging war?

- 3DIC war lost

- OSATs invested aggressively in 3D packaging and related technologies but the return was slow

- Taiwan OSATs are leveraging their strengths and pivoting towards the new CPO architectures before COUPE scales

- Competitive threat

- Customer pull

## Gaps and needs for Taiwan's CPO development

- CPO electrical—optical co-design integration

- High-yield optical coupling & assembly

- Supply chain fragmentation

- Talent and design ecosystem

- Laser integration & heterogeneous bonding

- Testing and yield challenges

#### Current status in Taiwan

- Silicon photonics chip test yield: 10%–70%

- Fiber-to-silicon chip coupling loss: > ±2.5 dB

- Multicore (22–40) fiber module

- Packaging process complexity

- Active vs. passive alignment

- Epoxy or solder fixation: Adhesive-induced misalignment

- Limited yield improvement capability (due to lack of optical expertise and proper debugging tools)

- Diverse solutions from vendors, OEMs, and customers prevent OSAT engineering resources from being focused

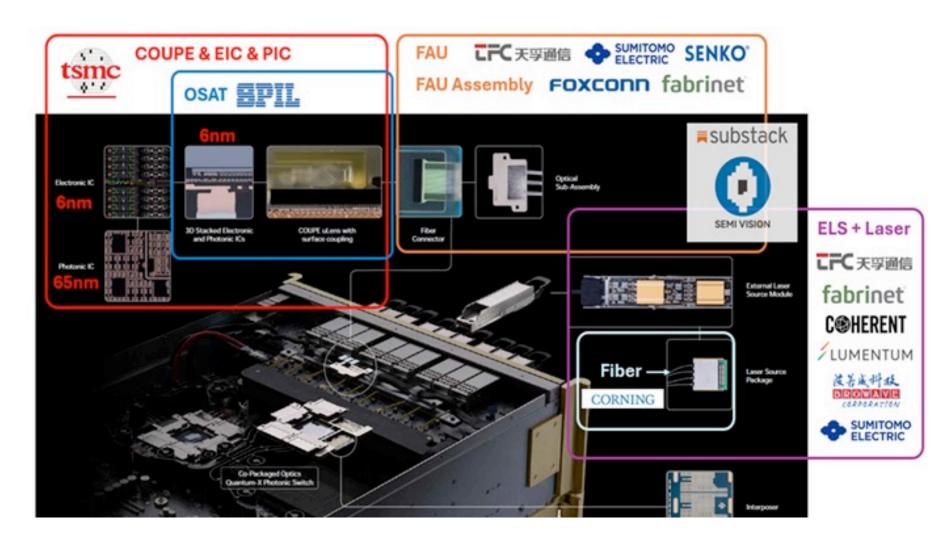

## Nvidia CPO supply chain

# Nvidia CPO supplier locations

| Item            | Company  | Country |  |

|-----------------|----------|---------|--|

| Wafer photonics | TSMC     | Taiwan  |  |

| CPO OSAT        | SPIL     | Taiwan  |  |

|                 | TFC      | China   |  |

| FAU             | Sumitomo | Japan   |  |

|                 | SENKO    | Japan   |  |

|                 | Fabrinet | USA     |  |

| ELS             | Lumentum | USA     |  |

| ELS             | Coherent | USA     |  |

|                 | Browave  | Taiwan  |  |

| System          | Foxconn  | Taiwan  |  |

Taiwan: 4

USA: 3

Japan: 2

China: 1

Europe: 0

# Advantages of developing business in Taiwan

- Taiwan possesses a comprehensive and fully developed semiconductor manufacturing ecosystem.

- Taiwan has strong momentum and sufficient capacity to drive the development of the CPO industry.

Taiwan lacks sufficient knowledge and talent in photonics-related technologies, and must leverage external expertise and new technologies to accelerate CPO development and surpass global competitors in this field.